3个实用方法避免电路中的闩锁效应

更新时间:2026-03-14 16:45:21

晨欣小编

电路中的闩锁效应(Latch-up)是一种不可逆的、非正常的电流路径,通常由于CMOS(互补金属氧化物半导体)器件中PNPN结构的存在而引起。以下是三种实用的方法,可以帮助避免电路中的闩锁效应:

1. 使用抑制器件或设计技术:

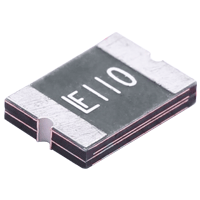

添加抑制器件: 将专门设计用于抑制闩锁效应的器件,如快速恢复二极管(Schottky二极管)等,连接到电路中的关键节点,以限制异常电流的流动。

布局和布线优化: 通过巧妙的布局和布线设计,减小关键信号线上的电流环,减缓或阻止闩锁效应的形成。

电源和接地设计: 优化电源和接地网络,降低共模噪声,并确保电源和接地的稳定性,以减小发生闩锁的概率。

2. 合理选择元件和工艺:

CMOS工艺改进: 选择具有改进抑制闩锁效应的CMOS工艺。一些现代CMOS工艺已经在设计上采取了一些措施来减轻闩锁效应。

CMOS电压调整: 合理选择CMOS器件的工作电压,以降低器件发生闩锁的概率。

选择适当的器件: 在关键位置选择抗闩锁性能较好的器件,以降低整个电路发生闩锁的可能性。

3. 添加外部保护电路:

电流限制器: 在关键节点添加电流限制器,可以有效限制异常电流的流动,降低闩锁效应的风险。

过压保护: 添加过压保护电路,以防止器件过载,减小因过电压引起的闩锁风险。

过温保护: 添加过温保护电路,防止器件过热,减小因过温引起的闩锁风险。

注意事项:

进行严格的电路设计和模拟分析,特别是在高功率或高频率应用中。

仔细阅读器件的数据手册,了解器件的工作特性和抗闩锁设计。

使用工具进行仿真和验证,以确保电路在实际工作中不容易发生闩锁。

通过采取这些方法,可以有效减小电路中发生闩锁效应的风险,提高电路的可靠性和稳定性。

售前客服

售前客服