jk触发器的逻辑功能表

更新时间:2026-03-14 16:45:21

晨欣小编

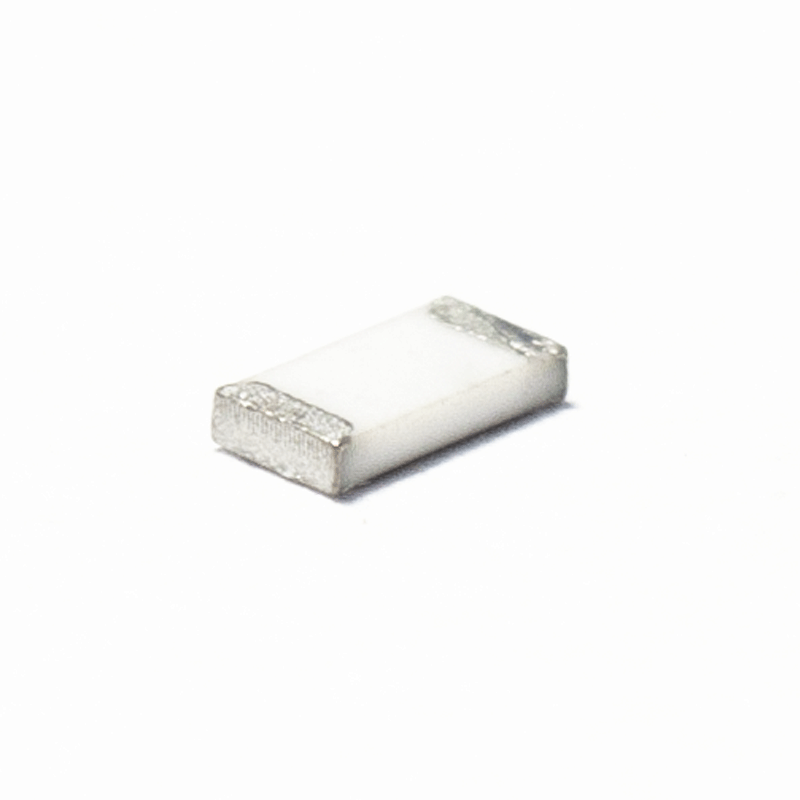

jk触发器是一种经典的数字电路元件,被广泛应用于计算机和电子设备中。它是由两个与门和一组反馈回路组成的,并在逻辑功能表中有着多种功能。

首先,jk触发器是一种双稳态触发器,它的状态可以处于两个稳定的状态之一:置位(Set)或复位(Reset)。当j和k输入信号同时为低电平时,保持之前的状态不变;当j输入为高电平,k输入为低电平时,将状态切换为置位;当j输入为低电平,k输入为高电平时,将状态切换为复位;而当j和k输入同时为高电平时,将触发器反转,即从置位状态切换到复位状态,或者从复位状态切换到置位状态。

除了存储状态的功能外,jk触发器还可以用来实现其他逻辑功能。根据不同的输入信号组合,jk触发器可以实现与门、或门、非门、异或门、边沿触发器等多种逻辑运算。

例如,当j和k输入信号同时为低电平时,相当于两个与门的输入端均为低电平,此时jk触发器的输出为与门的输出。而当j和k输入信号同时为高电平时,相当于两个与门的输入端均为高电平,此时jk触发器的输出为非门的输出。

另外,当j和k输入信号相同(都为高电平或都为低电平)且为正脉冲时,就能够产生边沿触发。边沿触发是指在触发器的输入端经过一次上升沿或下降沿时,其输出状态发生改变。这在时序控制电路中非常有用,可以用来实现时钟信号的延迟和触发等功能。

总之,jk触发器的逻辑功能表非常丰富,不仅可以存储二进制状态,还可以实现与门、或门、非门、异或门等多种逻辑运算,并且还能够实现边沿触发等时序控制功能。它在数字电路设计中扮演着重要的角色,为计算机和电子设备的正常运行提供了稳定和可靠的支持。

售前客服

售前客服