vhdl是什么意思_vhdl的作用_vhdl与verilog的区别

VHDL(VHSIC Hardware Description Language)即VHSIC硬件描述语言,是一种用于描述数字电路和系统的硬件描述语言。它是由美国国防部高级研究计划署(VHSIC)于1980年代初提出的,可以用于描述复杂的数字电路和集成电路。VHDL与Verilog是两种常用的硬件描述语言,在数字电路设计中起着重要的作用。

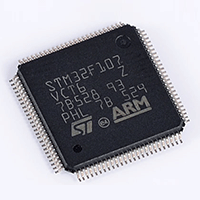

电子元器件品牌推荐:

H

VHDL的作用非常广泛。首先,它可以用于设计和描述数字逻辑电路。通过使用VHDL,工程师可以描述电路的结构、信号传输路径和控制逻辑。这样的描述可以用于仿真验证,以确保电路的正确性和功能。其次,VHDL还可以用于设计和描述通信协议,如UART、SPI和I2C等。这些协议在电子设备之间的通信中起到关键的作用,VHDL的应用使得协议的设计和验证更加方便和高效。

与Verilog相比,VHDL具有一些不同的特点和应用。首先,VHDL是由美国国防部开发和维护的,因此在军事和国防领域有着广泛的应用。其次,VHDL具有较强的表达能力和灵活性,可以描述更加复杂和抽象的电路和系统。然而,VHDL的学习和使用难度较高,需要掌握其独特的语法和规则。相比之下,Verilog更容易学习和使用,并且在硬件工程师和学术界中更为流行。

此外,VHDL和Verilog在一些细节上也存在一些差异。在语法上,VHDL更加强调面向对象的思想,使用过程和架构的方式来描述电路的结构和行为。而Verilog更加接近编程语言,使用模块和行为描述来表示电路的结构和功能。在仿真和综合方面,这两种语言也有一些不同的工具和方法。

综上所述,VHDL是一种广泛应用于数字电路设计和通信协议的硬件描述语言。它具有强大的表达能力和灵活性,但需花费更多的时间和精力来学习和掌握。与Verilog相比,VHDL在一些应用领域和细节上存在差异。但无论是VHDL还是Verilog,都是数字电路设计领域不可或缺的工具,为我们设计和实现各种各样的电子设备提供了有力的支持。我们期待未来VHDL和Verilog的进一步发展,为数字电路设计带来更多的创新和便利。

售前客服

售前客服